Os wafers de semicondutores são, literalmente, placas de silício circulares onde vários chips são impressos lado a lado em um processo óptico de altíssima precisão. As falhas são esperadas em procedimentos tão sensíveis, mas nem todas inviabilizam um componente, e a relação entre todos os chips impressos em um wafer e os efetivamente utilizáveis é o que determina o índice de aproveitamento.

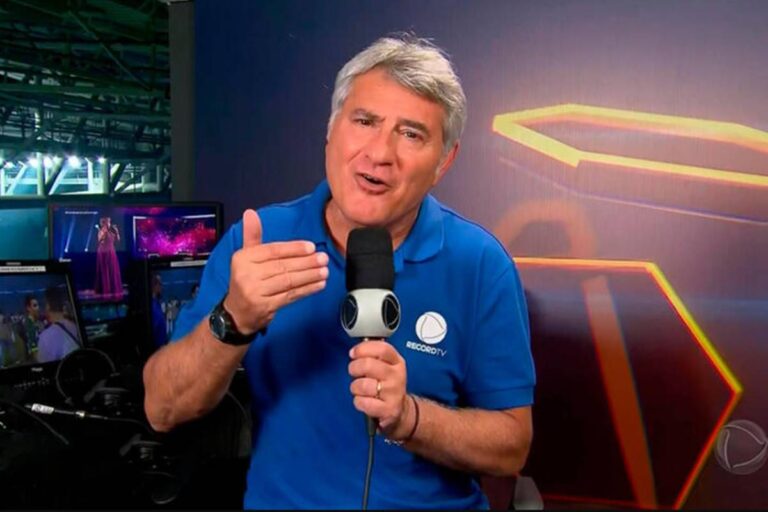

O Canaltech conversou com Yuri Daglian, Engenheiro de Aplicações da Intel Brasil, para entender melhor sobre o processo de fabricação dos chips de semicondutores e, principalmente, como os índices de aproveitamento afetam o portfólio de produtos e preços de cada segmento.

Continua após a publicidade

“O primeiro ponto que a gente precisa entender é que a base dos microprocessadores modernos é a utilização massiva de transistores. O transistor, na verdade, foi inventado muitos anos atrás, mas nos microprocessadores eles têm uma aplicação bastante interessante. Eles controlam o fluxo de elétrons no circuito; é como se eles fossem um interruptor muito pequeno”, explicou o engenheiro da Intel.

Como são fabricados os chips de semicondutores?

Essencialmente, o silício é a substância principal da areia, e sua abundância associada às suas propriedades condutivas fazem dele um excelente material para a fabricação de componentes eletrônicos.

Após ser aquecido a altíssimas temperaturas, o silício é despejado em moldes cilíndricos, que, ao se solidificarem, são fatiados em placas circulares finíssimas, mais próximas do padrão que chamamos de wafer.

Continua após a publicidade

“Para a gente, de fato, fabricar um processador a gente inicia com areia. Pode parecer estranho num primeiro momento, mas a areia é essencialmente silício, do ponto de vista químico. O silício é o principal semicondutor, tem propriedades muito boas e ele tem uma abundância muito grande. Areia é um material relativamente barato e tem propriedades interessantes, então ele acaba sendo muito útil.”

O próximo passo é relativamente mais complexo e envolve diversas etapas paralelas onde os chips são projetados efetivamente. Segundo Yuri, como estamos trabalhando com circuitos microscópicos, na escala de nanômetros – um milionésimo de milímetros -, seria inviável criar cada transistor individualmente.

Por essa razão, as fabricantes de chips desenvolvem os projetos da cada chip todo digitalmente e criam moldes nas mesmas proporções das placas de silício com centenas de chips idênticos posicionados lado a lado e distribuídos sobre toda a superfície desse “carimbo”.

Continua após a publicidade

“Essa areia é derretida, resfriada e ela vai formar um sólido. Esse sólido é fatiado em diversas ‘bolachas circulares’, e daí vem o nome do wafer. Esse wafer é colocado dentro de uma espécie de caixa que a Intel chama de FOUP, Front Opening Unified Pod. Dentro das fábricas da Intel, essas caixas vão transitar por uma série de equipamentos, em uma série de etapas muito complexas para esse wafer deixar de ser simplesmente um pedaço de silício e passar a ser, de fato, um circuito eletrônico”.

A etapa seguinte é, possivelmente, a mais sensível de todo o processo de fabricação de semicondutores, com esses moldes sendo transpostos para as placas de silício utilizando tecnologias de impressão ultravioleta. O resultado são as famosas “bolachas” ou “wafers” de semicondutores, que recebem esse nome pelo formato circular com muitos “quadradinhos”, cada um deles sendo uma pastilha individual de um chip.

“Uma das principais etapas desse processo é a da fotolitografia, que essencialmente é uma luz ultravioleta, de um certo comprimento de onda e frequência, que eu vou passar por uma máscara. Isso vai gravar um desenho nesse wafer, e quanto melhor a minha tecnologia desse feixe ultravioleta, melhor a qualidade do meu processador.”

Continua após a publicidade

Por que nem todos os chips são úteis?

Como estamos tratando de dimensões extremamente pequenas em uma impressão baseada em feixes de luz de altíssima frequência, as variáveis que podem gerar falhas são diversas, desde a temperatura do ambiente, interferência de iluminação externa, vibrações e assim por diante.

Vale ressaltar que as falhas estão previstas em todo projeto de engenharia, e por isso algumas estratégias permitem contornar problemas eventuais. Como estamos tratando de “interruptores” para liberar ou bloquear a passagem de corrente, é possível que, mesmo que alguns deles não sejam impressos corretamente, o chip final ainda consiga operar, apenas não nas suas condições ótimas.

Continua após a publicidade

“Todo o processo de fabricação em massa, e não só semicondutores, vai ter que passar por um processo de controle de qualidade, porque é inevitável, algumas unidades vão apresentar defeitos. Então eu tenho um pequeno desajuste de uma máquina, uma pequena imperfeição, uma pequena impureza que atuou naquele determinado momento. Por isso nem todos os chips podem ser aproveitados no final devido a esse tipo de defeito, que é esperado em um certo percentual, principalmente quando a gente fala de transistores de dimensões nanométricas, então qualquer defeito acaba tendo um impacto significativo”.

Por outro lado, se os circuitos comprometidos são cruciais para aquele chip, aquela pastilha precisa ser descartada, podendo impactar a viabilidade comercial daquele produto.

Como o índice de aproveitamento afeta o custo dos chips?

Tanto por isso, a etapa de controle de qualidade dos chips é essencial, pois nela as fabricantes definem quais pastilhas estão completamente inutilizadas, quais podem trabalhar no limite máximo do projeto original, além dos diferentes patamares de desempenho possíveis entre esses dois extremos.

Continua após a publicidade

Mesmo projeto, vasto portfólio

Isso significa que o projeto de um processador Intel Core de 14ª geração, Raptor Lake Refresh, por exemplo, é exatamente o mesmo para todos os produtos da série, do Core i3 ao Core i9. Dentro dos segmentos ainda existem subdivisões, também baseadas no índice de falhas dos wafers, representadas pelas letras ao final do modelo, como Core i9-14900T, i9-14900K ou i9-14900KF.

“Dependendo de onde um defeito atuar [na minha linha de produção], o chip vai ficar completamente inviabilizado, mas, dependendo do componente, eu ainda consigo aproveitar aquele chip. Não necessariamente na mais alta performance, mas no chip um pouco mais de entrada, sem prejuízo nenhum para o usuário. Onde [no wafer] pode ter mais defeito? Não tem uma correlação, não existe uma ‘zona ótima’ onde ocorrem menos defeitos, eles podem ocorrer em qualquer parte do wafer por uma série de razões.”

Dessa forma, o preço final do chip RLR é pautado pelos custos envolvidos na fabricação do topo de linha, com os demais segmentos ficando mais baratos de acordo com seu desempenho teórico limite.

Continua após a publicidade

“Para eu viabilizar qualquer tipo de produto, eu preciso ter uma economia de escala, precisa ter um volume, eu preciso pensar nos índices de defeito que eu vou ter na minha fabricação. O que é mais inteligente, fazer um projeto individual pro meu chip high-end, um outro projeto totalmente diferente pro meu chip intermediário, e um terceiro projeto pro meu chip low-end, sabendo que se eu tiver um defeito em qualquer um deles, eu vou ter que jogar o chip no descarte? Eu posso fazer um projeto para o meu chip high-end, e deixar dentro desse projeto uma certa tolerância do seguinte tipo: se tiver um defeito que atinja 2 cores, por exemplo, eu ainda consigo utilizar esse chip, só não vai ser o high-end, vai ser o mid, ou de entrada. Eu preparo o meu processo para isso, em vez de eu ter que descartar todos os chips com defeito, pode ser que eu precise descartar apenas 20%. Os outros 80% eu consigo utilizar em produtos um pouco mais de entrada, então esse processo é super importante para viabilizar a economia de escala e para eu conseguir entregar produtos bons com nível de qualidade alta, mas num custo mais baixo para o meu cliente final”

Como melhorar o índice de aproveitamento dos wafers?

Algo que é muito importante esclarecer é que cada wafer de silício traz apenas chips idênticos. Por anos, isso não fazia muita diferença, pois os chips eram monolíticos, com todos os componentes daquele processador impressos em um mesmo molde.

Continua após a publicidade

Arquitetura desagregada

Com a chegada dos processos de empacotamento avançado, com vários chiplets combinados em um mesmo processador, é preciso um molde para cada uma dessas pastilhas. Em outras palavras, os novos processadores Intel Core Ultra são fabricados utilizando vários wafers diferentes: um para a CPU, um para a iGPU Intel Arc, um para a NPU e assim por diante para cada componente modular.

“Uma vez que eu tenho uma arquitetura desagregada, diferente do chip monolítico de antes que eu tinha que produzir inteiros na mesma litografia, eu consigo produzir partes do chip em litografias diferentes. Isso faz com que não precise que todo meu processador incorra nesse custo maior de fabricação.”

Continua após a publicidade

Essa é uma das primeiras estratégias para melhorar o índice de aproveitamento, não necessariamente de cada wafer, mas de uma linha de produtos. Isso porque os diferentes chiplets não utilizam, necessariamente, a mesma litografia justamente por não existir essa obrigatoriedade.

Litografias diferentes para componentes diferentes

Trabalhar com chips modulares permite fabricar pastilhas específicas em litografias mais “maduras” nas quais o aproveitamento já é bastante superior. As novas litografias, menores, com menos tempo de testes, pesquisa e evolução, são mais caras e utilizadas apenas nos componentes que exigem aquela tecnologia.

“Pode ser que apenas a parte a pastilha da CPU precise de uma litografia mais avançada, mas a pastilha de I/O pode ser feita numa litografia mais madura, ou a GPU numa litografia um pouco diferente. Dessa forma, eu consigo balancear os custos de fabricação e, ao mesmo tempo, consigo acertar minha litografia por foco de uso”.

Continua após a publicidade

Com isso, um mesmo processador será fabricado combinando chips de wafers diferentes, fabricados em tecnologias com aproveitamentos diferentes, diluindo radicalmente eventuais perdas. Outra forma de melhorar o aproveitamento é investindo em equipamentos mais precisos, com lentes melhores, tecnologias de irradiação mais avançadas, e assim por diante.

Atualmente, a maioria das empresas já está utilizando equipamentos com tecnologia Extreme Ultraviolet (EUV), e o próximo passo na escala é partir para os EUV High-NA, com lentes de maior abertura numérica.

Resumidamente, todo salto tecnológico no desenvolvimento da computação irá implicar potencialmente no volume esperado de falhas para um wafer, mas isso só é um problema real quando essas falhas são tão graves que boa parte dos chips são completamente inutilizados.

Nesse aspecto, a própria corrida por miniaturizar rapidamente os semicondutores acaba sendo um fator prejudicial para as fabricantes. Adotar novas tecnologias para reduzir a escala dos componentes sem tempo hábil para amadurecer aquele processo, muitas vezes se torna uma aposta que no próximo estágio os índices iniciais sejam melhores para compensar os custos do investimento, o que nem sempre ocorre.